Consists of RAM and secondary memory.

In Von Neumann architecture, both data and instructions are stored in the same memory. In Howard Aiken’s architecture, data and instructions are stored in separate memories.

Memory cell

Section titled “Memory cell”Basic element of a semiconductor memory. Carries two stable states: 1 and 0. State can be read or written.

Memory chip

Section titled “Memory chip”Contains a 2D array of memory cells. A memory chip’s size is mentioned as "". is the number of words, and is the size of a word.

Number of bits written to/read from a chip simultaneously.

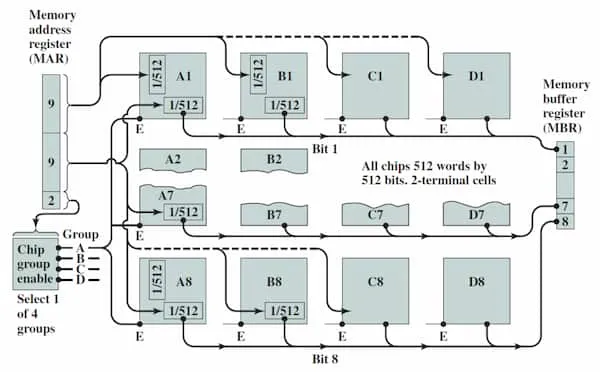

Memory module

Section titled “Memory module”Collection of memory chips.

Memory types

Section titled “Memory types”Volatile. High-speed read and write. Can either be dynamic (built using capacitors) or static (built using flip flops).

- SRAM: built using flip flops. expensive. faster. used for caching.

- DRAM: built using capacitors. cheaper. slower. used for main memory. needs constant refreshing.

Non-volatile memory.

| Memory Type | Category | Erasure | Write Mechanism |

|---|---|---|---|

| Read-only memory (ROM) | Read-only | Not possible | Masks |

| Programmable ROM (PROM) | Read-only | Not possible | Electrically |

| Erasable PROM (EPROM) | Read-mostly | UV light, chip-level | Electrically |

| Electrically Erasable PROM (EEPROM) | Read-mostly | Electrically, byte-level | Electrically |

| Flash memory | Read-mostly | Electrically, block-level | Electrically |

Designing a memory module

Section titled “Designing a memory module”For example, to build a module with chips:

- Total number of chips required: chips

- Size of address space: addresses

- Number of bits for address bus: bits