Half Adder

Section titled “Half Adder”A digital circuit component that adds 2 bits. Outputs 2 bits: sum bit and carry bit.

Full Adder

Section titled “Full Adder”A digital circuit component that adds 3 bits. Outputs 2 bits: sum bit and carry bit. An extension of the half adder where the carry bit of a half adder is input to another half adder. Built using 2 half adders.

Ripple Carry Adder

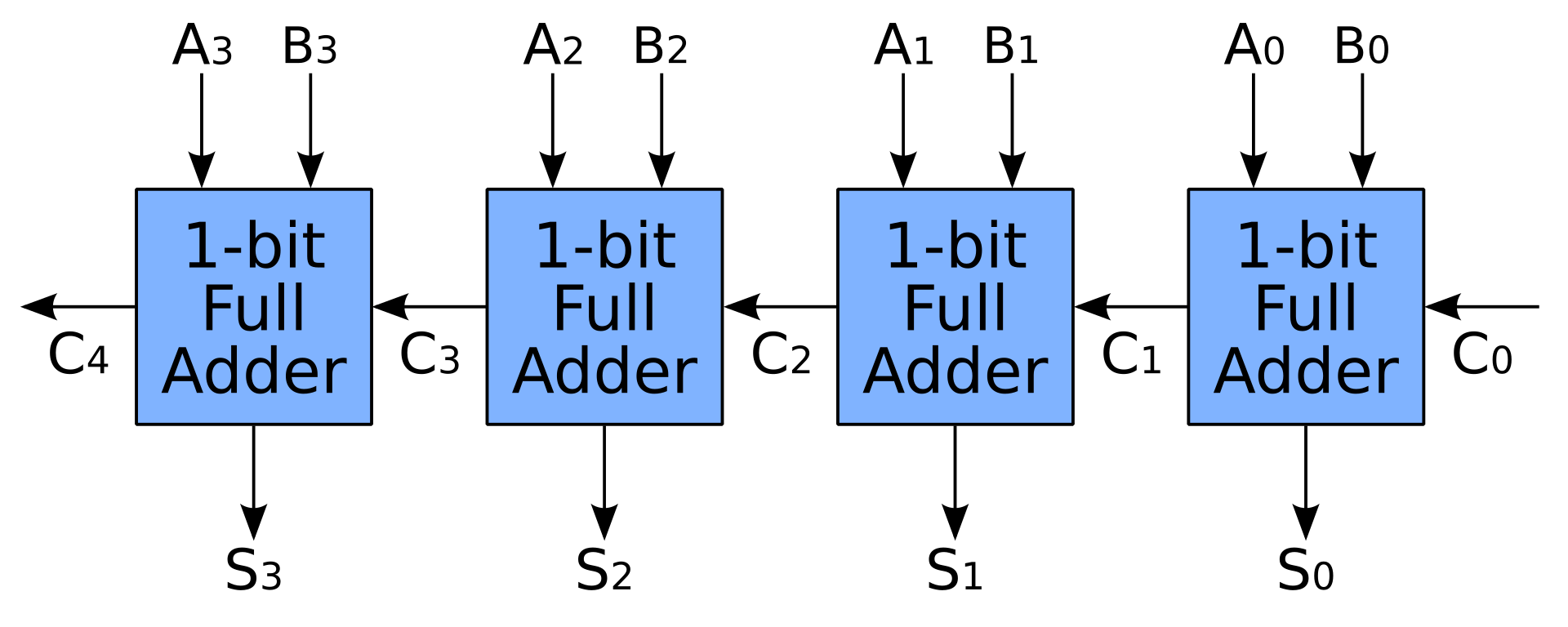

Section titled “Ripple Carry Adder”Made by a chain of full adders joined as mentioned below:

Image from Wikipedia.

Carry output of each FA ripples forward to calculate the output. Delay increases with number of bits.

Carry Lookahead Adder

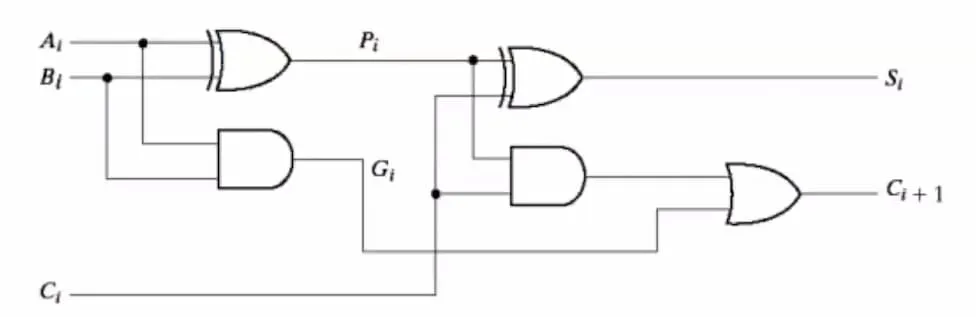

Section titled “Carry Lookahead Adder”A technique to speedup binary addition by calculating carry bits in parallel. In a CLA:

- Carry generate - means

C_outwill be created - Carry propogate - means

C_inwill be sent out asC_out

The CLA can be used to create n-bit adders which only have 3 level delay. Faster than RCA.

3 levels of delay:

- Generate & propagate signals

- Carry lookahead (sum-of-products)